- 您现在的位置:买卖IC网 > Sheet目录3872 > PIC18F4450T-I/ML (Microchip Technology)IC PIC MCU FLASH 8KX16 44QFN

150

XMEGA A [MANUAL]

8077I–AVR–11/2012

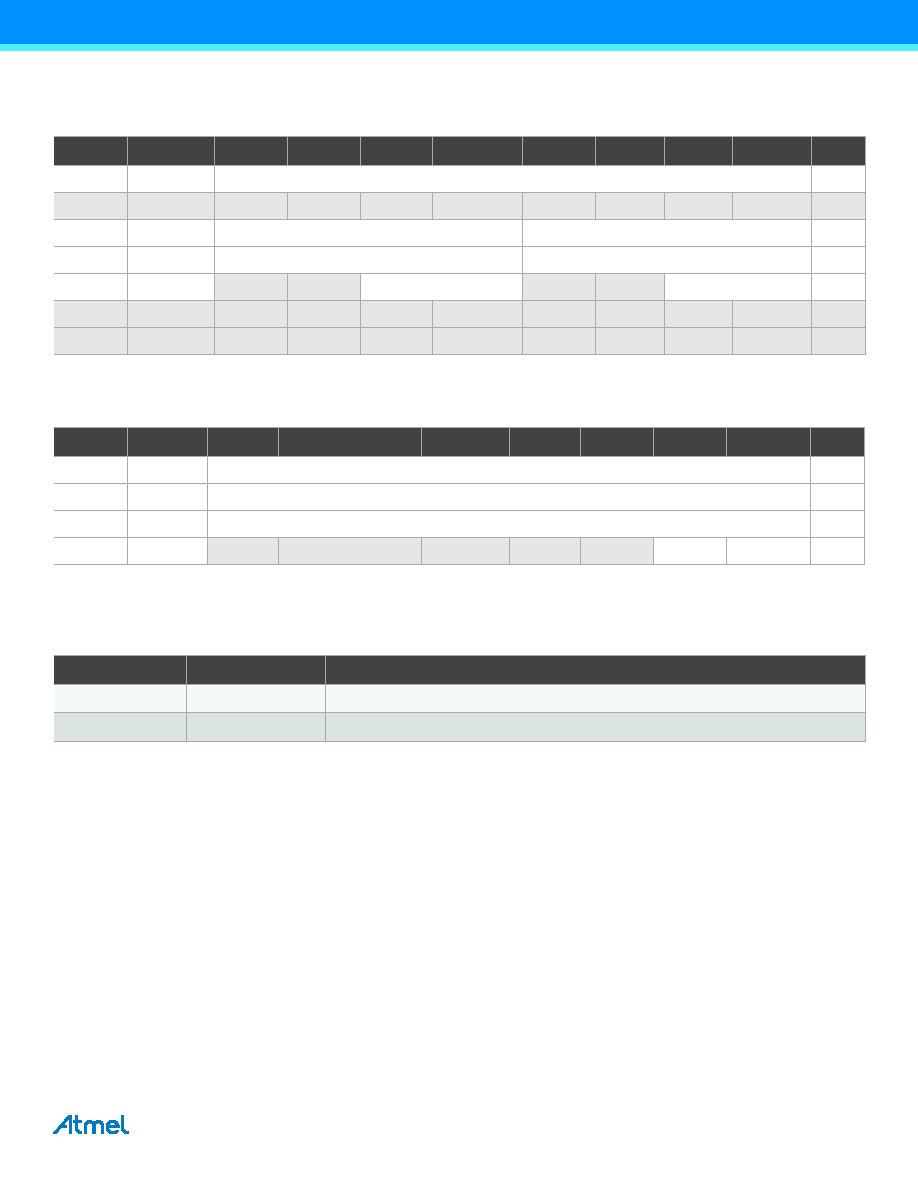

13.17 Register Summary – Port Configuration

13.18 Register Summary – Virtual Ports

13.19 Interrupt Vector Summary – Ports

Table 13-10. Port interrupt vectors and their word offset address.

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Page

+0x00

MPCMASK

MPCMASK[7:0]

+0x01

Reserved

–

+0x02

VPCTRLA

VP1MAP[3:0]

VP0MAP[3:0]

+0x03

VPCTRLB

VP3MAP[3:0]

VP2MAP[3:0]

+0x04

CLKEVOUT

–

EVOUT[1:0]

–

CLKOUT[1:0]

+0x05

Reserved

–

+0x06

Reserved

–

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Page

+0x00

DIR

DIR[7:0]

+0x01

OUT

OUT[7:0]

+0x02

IN

IN[7:0]

+0x03

INTFLAGS

–

INT1IF

INT0IF

Offset

Source

Interrupt description

0x00

INT0_vect

Port interrupt vector 0 offset

0x02

INT1_vect

Port interrupt vector 1 offset

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F4321T-I/ML

IC PIC MCU FLASH 4KX16 44QFN

PIC18F4221T-I/ML

IC PIC MCU FLASH 2KX16 44QFN

PIC18F2321T-I/ML

IC PIC MCU FLASH 4KX16 28QFN

PIC18F2221T-I/SO

IC PIC MCU FLASH 2KX16 28SOIC

PIC16LF1939-I/MV

IC MCU 8BIT 28KB FLASH 40-UQFN

PIC24F16KL402-I/SP

IC MCU 16BIT 16KB FLASH 28-SPDIP

PIC18F24J11-I/SS

IC PIC MCU FLASH 16K 2V 28-SSOP

PIC24F16KA101-I/SO

IC PIC MCU FLASH 16K 20-SOIC

相关代理商/技术参数

PIC18F4450T-I/PT

功能描述:8位微控制器 -MCU 16KB FL 768 RAM 34 I/O FS-USB 2.0 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-BL

制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER, FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER, FOR FLASHLAB; Silicon Manufacturer:Powerlite Systems; Core Architecture:PIC; Kit Contents:Board; Features:Bootloader Programming, RS232 Connector for Boot-Loading and Serial Comms ;RoHS Compliant: Yes

PIC18F4455-I/ML

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-I/P

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-I/PT

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455T-I/ML

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455T-I/PT

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4458-I/ML

功能描述:8位微控制器 -MCU 24KB Flash 2KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT